毕业论文(设计)基于FPGA 的图像光纤传输系统设计05571.doc

毕业论文(设计)基于FPGA 的图像光纤传输系统设计05571.doc

《毕业论文(设计)基于FPGA 的图像光纤传输系统设计05571.doc》由会员分享,可在线阅读,更多相关《毕业论文(设计)基于FPGA 的图像光纤传输系统设计05571.doc(6页珍藏版)》请在三一办公上搜索。

1、基于FPGA的图像光纤传输系统设计董林粒 郭大江(1. 2 成都理工大学信息科学与技术学院,成都 610059)摘要:提出一种基于FPGA和光纤的图像传输系统,阐述使用Lattice公司的FPGA和SDRAM构建图像缓存模块以及使用其内嵌的高速串口(SERDES)代替传统的串并转化器来完成图像光纤传输的方法。着重介绍系统的硬件设计和基于的FGPA的相关实现技术。关键词:FPGA,光纤传输系统,高速串口,图像缓存,DDR2 SDRAMAbstract: This paper present an image transmission system based on FPGA and optica

2、l fiber,introduces the use of Lattices FPGA and SDRAM to construct image cache module and the use of the SERDES embedded in FPGA take place of the traditional methods of SERDES to complete image transmission. Focuses on the systems hardware architecture design and image processing technology based o

3、n FPGA .Keywords: FPGA,Optical fiber transmission system,SERDES,Image Cache,DDR2 SDRAM0 引言DVI传输是将数字信号直接传送到显示设备上,因此它的速度较快,信号衰减较小,图像比较清晰的特点。但是进行远距离图像传输时,由于DVI信号衰减较大,影响图像传输质量。光纤传输具有损耗低、抗干扰性强、带宽高、传输距离远等特点,现在应用越来越广泛。本系统将DVI的图像数据转换成光信号后,通过光纤进行远距离传输,这样可以及避免DVI信号传输的缺点。随着半导体工艺的快速发展,一些主流的FPGA芯片在逻辑资源、性能、速度以及可靠

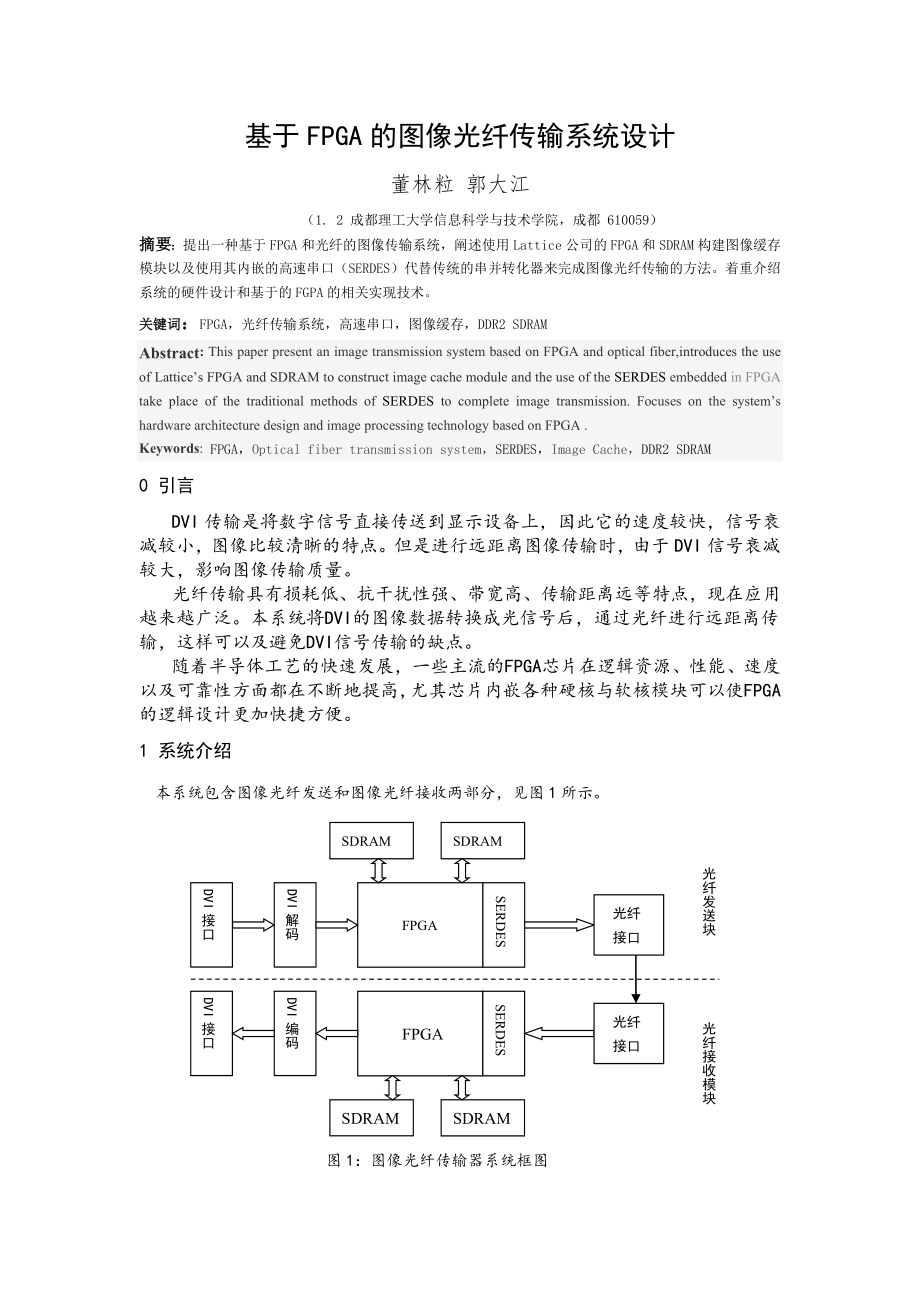

4、性方面都在不断地提高,尤其芯片内嵌各种硬核与软核模块可以使FPGA的逻辑设计更加快捷方便。1 系统介绍本系统包含图像光纤发送和图像光纤接收两部分,见图1所示。DVI接口DVI解码FPGASDRAMSERDESFPGASERDESDVI接口DVI编码SDRAMSDRAMSDRAM光纤发送块光纤接收模块光纤接口光纤接口 图1:图像光纤传输器系统框图整个光纤传输系统的工作流程:在发送端,前端DVI解码部分将DVI信号解码成YUV或者RGB格式的并行数据流后送至FPGA,FPGA与片外的SDRAM完成图像数据缓存,并且FPGA内嵌的高速串口(SERDES)将缓存数据进行并串转换形成高速串行数据,然后将

5、数据发送出去,光纤模块接收到数据后,将电信号转化成光信号通过光纤传输。在接收端,工作流程与发送端相反,先是光纤模块将光信号转化成电信号后送给FPGA,FPGA内嵌的SERDES模块将高速串行数据进行串并转换后送给图像缓存模块,然后DVI编码模块对图像缓存模块中的数据完成DVI信号编码。2 系统设计整个图像光纤传输系统设计的关键在于FPGA硬件设计、图像缓存部分设计、串并转换逻辑、光纤模块设计和FIFO控制设计,由于DVI解码模块和编码模块比较成熟,限于篇幅原因不在本文讨论之列。2.1 FPGA硬件设计如图1所示,FPGA作为系统的核心部件,主要完成数据的串并转换、数据缓存以及编解码逻辑控制等功

6、能,其核心任务是3G-SDI接口设计和基于双端口存储器(Embedded Block RAM)的FIFO设计。 系统考虑到逻辑资源容量、I/O接口、以及与SDRAM连接High-speed I/O资源等情况后,选用Lattice公司ECP3-35-484,该器件具有33K的LUTs(逻辑单元)、295个可配置IO引脚、丰富的PLL和DLL资源、支持SDRAM的High-Speed IO接口、以具有4个通道的Embedded SERDES,满足系统需求。Lattice公司ECP3系列FPGA内嵌的SERDES模块是一种高速串行收发器,支持高达3.125G/s的3G-SDI信号传输、支持8B/10

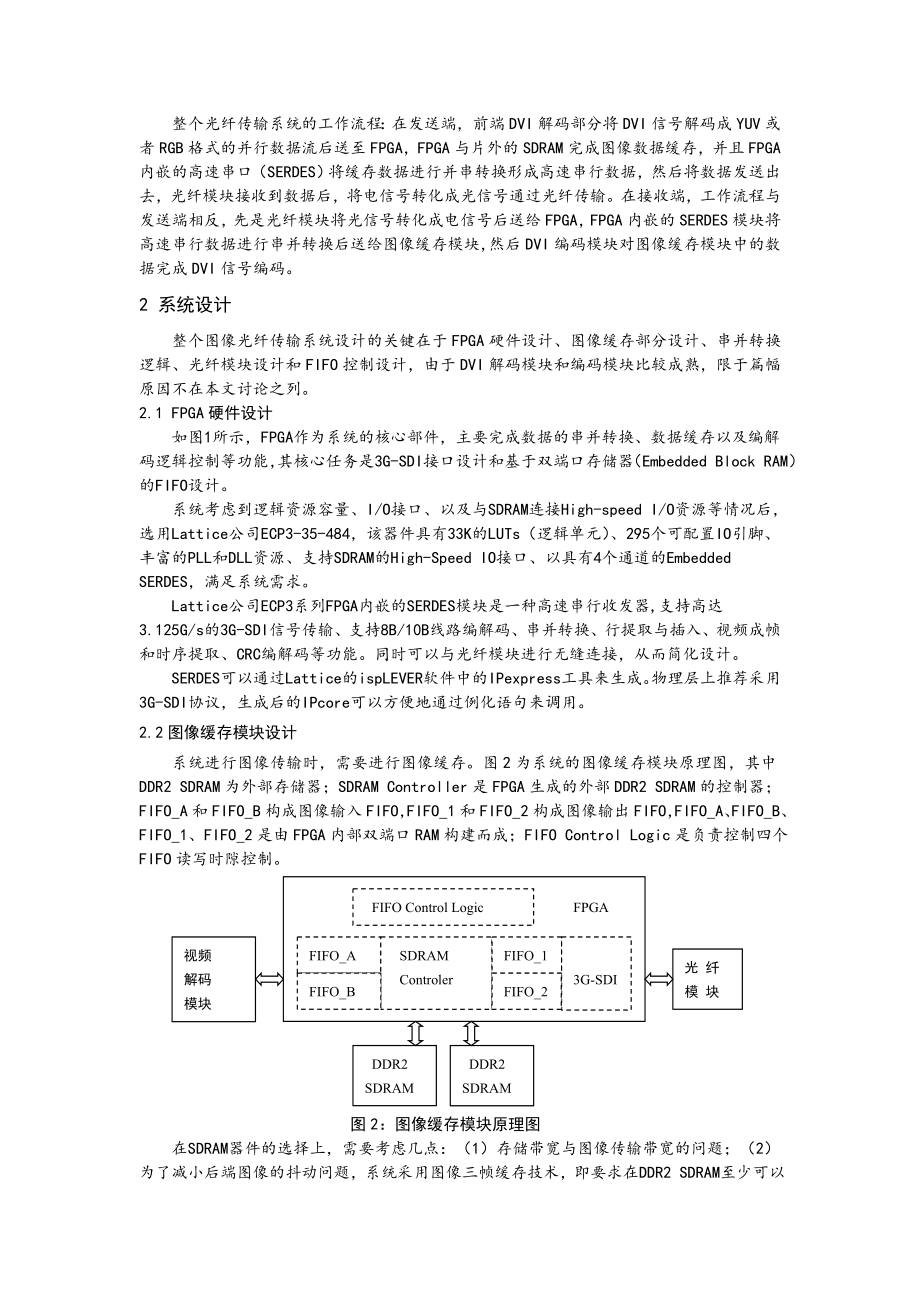

7、B线路编解码、串并转换、行提取与插入、视频成帧和时序提取、CRC编解码等功能。同时可以与光纤模块进行无缝连接,从而简化设计。SERDES可以通过Lattice的ispLEVER软件中的IPexpress工具来生成。物理层上推荐采用3G-SDI协议,生成后的IPcore可以方便地通过例化语句来调用。2.2图像缓存模块设计系统进行图像传输时,需要进行图像缓存。图2为系统的图像缓存模块原理图,其中DDR2 SDRAM为外部存储器;SDRAM Controller是FPGA生成的外部DDR2 SDRAM的控制器; FIFO_A和FIFO_B构成图像输入FIFO,FIFO_1和FIFO_2构成图像输出F

8、IFO,FIFO_A、FIFO_B、FIFO_1、FIFO_2是由FPGA内部双端口RAM构建而成;FIFO Control Logic是负责控制四个FIFO读写时隙控制。FIFO_ASDRAMControlerFIFO_1DDR2SDRAMFIFO Control LogicDDR2SDRAM视频解码模块光 纤模 块FPGA3G-SDIFIFO_BFIFO_2图2:图像缓存模块原理图在SDRAM器件的选择上,需要考虑几点:(1)存储带宽与图像传输带宽的问题;(2)为了减小后端图像的抖动问题,系统采用图像三帧缓存技术,即要求在DDR2 SDRAM至少可以存储三帧图像数据,因此要考虑存储深度问题

9、;(3)考虑如1080P的高清分辨率的图像传输对存储带宽的要求。基于以上几点考虑,系统使用两片尔必达公司生产的型号为EDE5116AJBG1的DDR2 SDRAM,该芯片为32M*16bit,两片即可构成32M*32bits深度的图像缓存系统。DDR2 SDRAM器件具有价格低、容量大、速度较快,非常适合用于图像处理系统。但其控制逻辑时序较复杂,要求一个接口的控制器,这需要通过FPGA内部逻辑来生成。DDR2 SDRAM控制器是图像缓存模块设计的关键。ECP3系列FPGA内部的High-speed IO支持DDR2 SDRAM电气标准。并且该控制器也可以通过ispLEVER软件中的IPexpr

10、ess工具来生成,生成后的IPcore可以通过例化语句来调用。2.3 光纤模块设计光纤通信以其损耗低、带宽充裕、抗电磁干扰、保密性好及寿命长等特点受到越来越多的青睐。光纤模块主要作用完成光信号的发送与接收,即在发送端将经过FPGA处理后的逻辑电平信号转换成光信号;在接收端将光信号转换成逻辑电平信号后送给FPGA进行相关处理。本系统选用Finisar公司型号为FWLF1524P2yxx的SFP光纤模块,该模块为单模光纤、采用SFP封装、收发一体、带宽达到4.25Gb/s、损耗低、传输距离可以达到30Km左右,适合中远距离图像信号传输。同时该模块支持3G-SDI协议,可以与FPGA进行无缝连接。该

11、模块兼容1G/2G/4G 光纤通道协议,具有良好的EMI性能。2.4 FIFO模块设计如图2所示,FIFO和FIFO Control Logic在图像缓存模块中比较重要,FIFO硬件可以使用ispLEVER软件中的IPexpress工具来生成,生成后的IPcore可以方便地通过例化语句来调用。而FIFO Control Logic 是主要协调各个FIFO的读写及时序控制,需要通过状态机逻辑来生成。FIFO_1、FIFO_2、FIFO_A和FIFO_B采用Lattice FPGA内嵌的伪双端口RAM来构建,因此FIFO_A和FIFO_B不能同时读写,否则输出数据可能是个不确定值。为了提高图像数据

12、的缓存效率,输入输出FIFO使用两个FIFO来完成读写;每个FIFO执行缓存操作,即每个数据一次的读写数据为一行的图像数据存,因此四个FIFO存储深度设置为1920,位宽为32bits。HS_Control写地址产生逻辑写地址写使能读使能读地址CLK_RCLK_W读控制写控制读数据写数据FIFOControlLogicFIFO双端口RAMDDR2SDRAM图 像数 据读地址产生逻辑图3:FIFO读写切换控制原理图图3是FPGA内部控制两个FIFO的读写切换的原理图。CLK_W是DVI解码芯片输出的图像像素时钟,CLK_R是DDR2 SDRAM的时钟。HS_Control来自DVI解码输出的图像

13、行同步信号,该信号作为FIFO Control Logic读写切换的控制出发信号,通过对该信号的逻辑处理产生相位相反的写使能和读使能信号,然后去分别去控制读、写地址产生逻辑,从而完成数据传输,并完成两个FIFO的切换。3 结论本图像传输系统采用高性能的FPGA作为系统核心,利用FPGA内嵌的高速串口完成串并转换,取代了传统上采用分立元件设计高速传输系统的方法, 简化了电路设计, 减少了元器件间的互连,而且系统可靠性、稳定性和灵活性都更高。同时系统采用光纤进行图像传输通信,具有损耗低、抗电磁干扰能力强、传输距离远等特点。实验证明该系统的设计是成功的,并且在高速数据采集、远程控制等方面也具有借鉴意

14、义。参考文献1.LatticeECP3 Family Data Sheet R. 2.LatticeECP3 High-Speed I/O InterfaceR.3.LatticeECP3 Memory Usage GuideR. tn1179.pdf4.LatticeECP3 SERDES/PCS Usage GuideR5.潘松,黄继业EDA技术使用教程M北京:科学出版社,20026.基于FPGA 的DRR2 SDRAM 控制器接口的简化设计方法及实现测试测量技术,2008 第11期作者简介董林粒,硕士研究生,专业为通信与信息系统,研究方向:图像处理及FPGA技术;郭大江,副教授,硕士生导

15、师,主要从事嵌入式系统和图像处理相关研究。第一作者:董林粒待添加的隐藏文字内容2性别:男,出生年月:1985年11月02日。单位:成都理工大学信息科学与技术学院。职务:硕士研究生郭大江性别:男,出生年月:1955年单位:成都理工大学信息科学与技术学院。职务:副教授,硕士生导师联系人:董林粒联系方式: 手机:18681226658邮箱:dong_linli联系地址:四川省成都市二仙桥东三段1号成都理工大学银2-214邮政编码:610059Editors note: Judson Jones is a meteorologist, journalist and photographer. He h

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 毕业论文设计基于FPGA 的图像光纤传输系统设计05571 毕业论文 设计 基于 FPGA 图像 光纤 传输 系统 05571

三一办公所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

三一办公所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

链接地址:https://www.31ppt.com/p-3974026.html